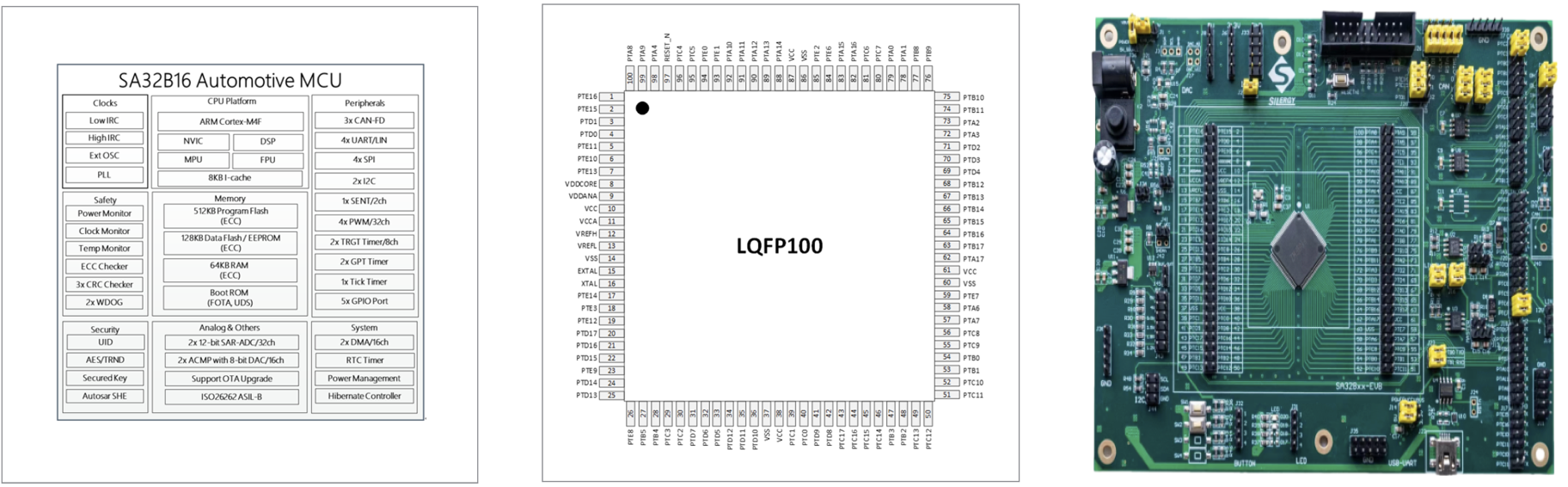

Features

• Kernel:

ARM Cortex-M4F, maximum support frequency: 120MHz, DSP, FPU, MPU, and NVIC, support JTAG and SWD debugging interface.

• Memory:

Code Flash: 512KB, Data Flash: 128KB, SRAM: 64KB, instruction Cache: 8KB.

• System:

The two DMA engines have a total of 16 channels to support more efficient data handling, with built-in internal signal interconnection modules, SysTick and RTC timers.

• Functional safety:

Support ISO26262 ASIL-B level, Flash and SRAM read band ECC function, on-chip clock monitoring, on-chip power supply overvoltage and undervoltage monitoring, on-chip temperature monitoring, 3 hardware CRC for data integrity verification, built-in independent clock WDOG.

• Information security:

SSE(SHE Security Engine) for encryption and decryption, supports AES128, SHA256, TRNG, secure key storage and unique ID, supports secure startup and AES-CMAC authentication, complies with AUTOSAR SHE standard, Comply with EVITA Light HSM specification.

• Simulation:

Support external crystal input: 8MHz~40MHz, built-in high precision HIRC: 24MHz, built-in low power LIRC: 131.072KHz, built-in PLL, ADC: 2 12bit@1Mbps SAR ADC, each ADC support 16-channel, analog comparison: Two fast comparators with built-in 8bit Dacs.

• Peripherals:

3 CAN, each supporting CAN 2.0 and CAN-FD, 4 UART/LIN, each supporting LIN2.2 and SAE J2602, 4 SPI, each with 4 slice selection signals, 2 I2C, 1 SENT, a total of 2 channels, 4 16-bit PWM, each PWM supports 8 channels

Flexible Trigger Timers (Two 32-bit TRGTS): Each TRGT supports four channels and two 16-bit General Purpose timers (GPT).

• Other features:

AEC-Q100 G1 grade (TA: -40 to 125°C), package: LQFP100, LQFP64.

EVB_SA32B1x

The EVB_SA32B1x evaluation board is used to evaluate the SA32B1x series of highly reliable automotive MCU chips based on the ARM Cortex-M4F core